Motorola MVME2700 Series Manuals

Manuals and User Guides for Motorola MVME2700 Series. We have 3 Motorola MVME2700 Series manuals available for free PDF download: Reference Manual, Installation And Use Manual

Motorola MVME2700 Series Reference Manual (283 pages)

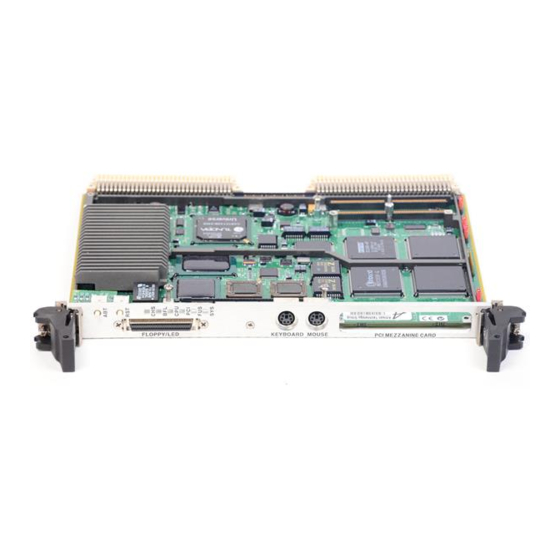

MVME2600/2700 Series Single Board Computer

Brand: Motorola

|

Category: Motherboard

|

Size: 0.86 MB

Table of Contents

-

Introduction18

-

Overview20

-

-

-

Overview24

-

-

-

Memory Maps25

-

-

-

-

Introduction68

-

Overview68

-

Requirements69

-

Features69

-

-

-

Registers89

-

-

PCI Registers108

-

Config_Address116

-

-

-

Architecture119

-

Introduction119

-

Compatibility121

-

Timers122

-

MPIC Registers128

-

Operation148

-

-

-

-

-

Introduction152

-

Overview152

-

Features152

-

-

Block Diagrams153

-

-

DRAM Speeds158

-

Rom/Flash Speeds162

-

DRAM Tester166

-

Refresh/Scrub171

-

DRAM Arbitration172

-

Chip Defaults173

-

CSR Accesses174

-

CSR Architecture175

-

Register Summary180

-

-

Bit Counter202

-

Test SRAM203

-

ECC Codes210

-

Data Paths212

-

-

-

-

Introduction216

-

-

-

-

Introduction236

-

Exceptions243

-

Endian Issues246

-

PCI Domain249

-

Pci-Scsi249

-

PCI-Ethernet250

-

PCI-Graphics250

-

-

Vmebus Domain250

-

Overview252

-

Advertisement

Motorola MVME2700 Series Installation And Use Manual (215 pages)

Table of Contents

-

-

Overview21

-

-

-

-

-

-

-

Overview85

-

Memory Maps88

-

-

DMA Channels94

-

-

-

Overview99

-

Features99

-

Block Diagram103

-

SCSI Interface104

-

SCSI Termination105

-

-

Vmebus Interface107

-

-

Interval Timers112

-

16-Bit Timers113

-

-

-

Z8536 CIO Device114

-

-

-

I/O Power119

-

-

MPC750 Processor120

-

Flash Memory120

-

-

Speaker Control120

-

-

-

-

-

SCSI Connector145

-

Serial Ports 1-4146

-

-

-

Overview155

-

Implementation156

-

Use the Debugger157

-

-

-

Introduction185

-

Proper Grounding193

-

Motorola MVME2700 Series Installation And Use Manual (200 pages)

MVME2700 Series Single Board Computer

Brand: Motorola

|

Category: Motherboard

|

Size: 2.46 MB

Table of Contents

-

-

-

Overview60

-

-

-

Overview79

-

Memory Maps82

-

-

-

Overview92

-

Features92

-

-

Parallel Port101

-

Interval Timers105

-

16-Bit Timers106

-

Z8536 CIO Device107

-

I/O Power112

-

Flash Memory113

-

-

-

Overview143

-

-

Introduction180

-

-

Proper Grounding187

-

-

Advertisement